#### IMPLEMENTATION OF POWER GATED ALU FOR LOW POWER PROCESSOR

K PRASAD BABU<sup>1</sup>, DR.K.E. SREENIVASA MURTHY<sup>2</sup>, DR. M.N. GIRI PRASASD<sup>3</sup> <sup>1</sup>15PH0426, Department of ECE, JNTUA, Anantapuramu, Andhra Pradesh, India, <u>kprasadbabuece433@gmail.com</u> <sup>2</sup>Pricipal & Professor, Department of ECE, RECW, Kurnool, Andhra Pradesh, India, <u>kesmurthy1969@gmail.com</u> <sup>3</sup>Director of Academics & Audit, Professor, Department of ECE, JNTUA, Anantapuramu, Andhra Pradesh, India, <u>giriprasadmn.ece@jntua.ac.in</u>

#### ABSTRACT

Low power designs are needed not only for moveable applications, but also to lessen power in high power systems. Power consumption can be miniaturize at the system level, architectural level, algorithm level, micro-architectural level, gate level, or circuit level. Power gating of functional system has proven to be a compelling approach to cut back power consumption. With the each requirement for high speed, low power consumption, and huge performance endure to increase year after year, devices must be scaled to lower dimensionality. Current technology sees power utilization as the restraining factor. A high power supply will affect the temperature, which will affect the cooling cost of the chip. In this work the power gated ALU with minimal functions is designed and implemented. Comparison is made with presence of nmos transistor and without it. 120nm technology is employed for the design. MOS model3 parameters with 120nm technology is used in the design.1-bit ALU, 4-bit ALU and 8-bit ALU are designed and implemented with power comparisons.

*Keywords:* Power-Gating, ALU, Low Power, 120nm, MOS model 3, Low Power Processor.

#### **1.** INTRODUCTION

With the advent of low power applications the need for effective techniques has been primary concern. Power gating is a technique used in VLSI design to reduce power consumption by turning off power to unused or idle circuits. It can be accomplished with PG cells, which reins the flow of power to certain parts of a chip. When a circuit is not in use, its power gating cell can be turned off, effectively cutting power to that circuit and reducing overall power consumption. The Power gated concept is widely employed at different sources, depending upon application type that can be Block level, Gate level/ device level. It is a widely used technique in low-power designs of processor which are used in mobile and IoT applications. Most of the Current processors employ the basic ALU which are designed & implemented using basic circuitry. They are designed to perform a wide range of operations quickly and efficiently, allowing the CPU to execute instructions and perform complex calculations. An Arithmetic Logic Unit is a digital circuit that performs arithmetic and logic operations on binary numbers. The ALU can be designed to perform a variety of operations, including addition, subtraction, multiplication, division, and logical operations such as AND, OR, and NOT. The specific design of the ALU will depend on the operations it needs to perform and the desired level of performance. the parameters are drastically changing with the advent in every year as shown in below figure

| Technology year                          | 2009                      | 2010 | 2011 | 2012 | 2013 | 2014 |  |

|------------------------------------------|---------------------------|------|------|------|------|------|--|

| Dimensions                               |                           |      |      |      |      |      |  |

| MPU Half-Pitch $(nm)^{\dagger}$          | 54                        | 45   | 38   | 32   | 27   | 24   |  |

| Physical Lgate (HP) $(nm)^{\dagger}$     | 29                        | 27   | 24   | 22   | 20   | 18   |  |

| Supply Voltage Parameters                | Supply Voltage Parameters |      |      |      |      |      |  |

| VDD $(HP)^{\dagger}$                     | 1.00                      | 0.97 | 0.93 | 0.90 | 0.87 | 0.84 |  |

| VDD $(LOP)^{\dagger}$                    | 0.95                      | 0.95 | 0.85 | 0.85 | 0.80 | 0.80 |  |

| Interconnect-Related Parameters          |                           |      |      |      |      |      |  |

| Capacitance $(pF/cm)^{\ddagger}$         | 1.75                      | 1.75 | 1.75 | 1.65 | 1.65 | 1.65 |  |

| Total length $(Km/cm^2)^{\ddagger}$      | 2.00                      | 2.22 | 2.50 | 2.86 | 3.13 | 3.57 |  |

| Transistor-Related Paramete              | rs                        |      |      |      |      |      |  |

| Ioff (HP) $(\mu A/um)^{\dagger\ddagger}$ | 0.17                      | 0.46 | 0.71 | 0.70 | 0.64 | 0.69 |  |

| Ioff (LSTP) $(pA/um)^{\dagger\ddagger}$  | 30.5                      | 30.7 | 30.2 | 30.2 | 30.9 | 31.7 |  |

| Cg,total (HP) $(fF/\mu m)^{\dagger}$     | 1.00                      | 0.97 | 0.93 | 0.95 | 0.96 | 0.75 |  |

Figure 1: ITRS parameters for previous years.

## 2. LITERATURE SURVEY

Below table is some of the findings made by doing literature survey.

| SL.NO | AUTHOR                                   | TITLE                                                                                                      | YEAR         | CONCEPT                                                 | METHOD                                                                     |

|-------|------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------------------|----------------------------------------------------------------------------|

| 1     | G.SARANYA,<br>R.S.<br>KIRUTHIKA          | Optimized Design Of<br>An Alu Block Using<br>Architectural Level<br>Of Power<br>Optimization<br>Techniques | Mar-<br>2011 | ALU<br>POWER<br>REDUCTIO<br>N                           | POWER<br>GATING                                                            |

| 2     | N.RAVINDR<br>AN,R.MARY<br>LOURDE         | An Optimum Vlsi<br>Design Of 16-Bit Alu                                                                    | Mar-<br>2015 | ALU<br>POWER<br>REDUCTIO<br>N                           | MIXED<br>LOGIC                                                             |

| 3     | GUANG-<br>MINGTANG,<br>KENSUKE<br>TAKATA | 4-Bit Slice Alu For<br>32-Bit Rsfq<br>Microprocessors                                                      | Jan-<br>2016 | ALU FOR<br>MIPS32<br>INSTRUCTI<br>ON SET                | SYNCHRON<br>OUS<br>CONCURRE<br>NT FLOW<br>CLOCKING                         |

| 4     | JINHUI<br>WANG, NA<br>GONG               | DCT for Low Power<br>Microprocessors                                                                       | Feb-<br>2016 | HIGHER<br>POWER<br>EFFICIENC<br>Y                       | P-TYPE/N-<br>TYPE<br>DYNAMIC<br>CIRCUIT<br>SELECTION<br>ALGORITHM<br>& FCR |

| 5     | YU-GUANG<br>CHEN,WAN-<br>YU WEN          | DLRSS For Low<br>Power Optimization                                                                        | Aug-<br>2016 | EXTENSIO<br>N OF<br>DYNAMIC<br>VOLTAGE<br>FREQUENC<br>Y | DLRS:<br>DYNAMIC<br>LOGIC<br>RECONFIGU<br>RABLE<br>STRUCTURE               |

Table 1. Literature Survey and methods employed.

Vol 12 Issue 01 2023

# BioGecko

|    |                                              |                                                                                                         |              | SCALING(D<br>VFS)                      |                                                                                                                                                             |

|----|----------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6  | CHRISTOPHE<br>R SCHAEF,<br>JASON T<br>STAUTH | Microprocessor Cores<br>Stacked in Vertical<br>Voltage using<br>Domains Efficient<br>Voltage Regulation | Feb-<br>2016 | EFFICIENT<br>VOLTAGE<br>REGUALTI<br>ON | POWER<br>CONVERSIO<br>N<br>TOPOLOGY<br>TO<br>MULTICORE<br>REGULATIO<br>N                                                                                    |

| 7  | CHENG-YEN<br>LEE,PING-<br>HSUAN<br>HSIES     | StndrdCellDesignFlowCompatibleEnergyRecyclingLogic                                                      | Jan-<br>2016 | LOW<br>POWER                           | ENERGY<br>RECYCLING<br>MICROARCH<br>ITECTURE &<br>ADIABATIC<br>LOGIC                                                                                        |

| 8  | AN-TAI<br>XIAO,YUNG-<br>SIANG MIAO           | A Variable Voltage<br>Low Power<br>Technique For Digital<br>Circuit System                              | Mar-<br>2016 | LOW<br>POWER                           | VOLTAGE<br>FREQUENCY<br>ADJUSTOR<br>(VFA) &<br>FREQUENCY<br>DUTY<br>CYCLE<br>ADJUSTOR(F<br>DCA)<br>CIRCUITS                                                 |

| 11 | HAKONTOR<br>EYIN,PAMEL<br>A T BHATTI         | LP ASIC Signal<br>Processor for a<br>Vestibular Prosthesis                                              | Jun-<br>2016 | LOW<br>POWER<br>PROCESSO<br>R          | COORDINAT<br>E SYSTEM<br>TRANSFOR<br>MATION TO<br>CORRECT<br>FOR<br>MISALIGNM<br>ENT<br>BETWEEN<br>NATURAL<br>SENSORS &<br>IMPLANTED<br>INERTIAL<br>SENSORS |

## Vol 12 Issue 01 2023

| 12 | SMITA<br>SINGHAL,NI<br>DHI GAUR          | Analysis &<br>Comparision Of<br>Leakage Power<br>Reduction Techniques<br>In Cmos Circuits           | Sep-<br>2015 | LEAKAGE<br>POWER<br>REDUCTIO<br>N<br>TECHNIQU<br>ES               | MULTI-<br>THRESHOLD<br>CMOS,<br>SUPER-<br>CUTOFF<br>CMOS,ZIGZA<br>Q,STACK<br>EFFECT,LEC<br>TOR,SLEEPY<br>STACK,SLEE<br>PY<br>KEEPER,DU<br>AL<br>SLEEP,SLEE<br>PY-PASS<br>GATE &<br>TRANSISTO<br>R GATING |

|----|------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13 | JEFFERSON<br>A<br>HORA,NIEVA<br>M MAPULA | For Ultra Low Power<br>Application Design<br>Of Rf To Dc<br>Converter In 90nm<br>Cmos Technology    | Dec-<br>2015 | ULTRA<br>LOW<br>POWER                                             | VOLTAGE<br>RECTIFIER<br>IS USED                                                                                                                                                                          |

| 14 | MANAS<br>SINGHAL,RA<br>JESH MEHRA        | Area Efficient Low<br>Skewed Even Parity<br>Generator Layout<br>Development                         | Dec-<br>2015 | AREA<br>EFFICIENC<br>Y                                            | UNSKEWED<br>&<br>LOSKEWED<br>TECHNIQUE<br>S                                                                                                                                                              |

| 15 | ANDRES<br>GOMEZ,CHRI<br>STIAN PINTO      | ReducingEnergyConsumptionInMicrocontroller-Based Platforms WithLow DesignMarginCo-Processors        | Oct-<br>2015 | ENERGY<br>MINIMIZA<br>TION<br>TECHNIQU<br>ES                      | DVFS,THER<br>MAL<br>MANAGEME<br>NT<br>TECHNIQUE<br>S                                                                                                                                                     |

| 16 | SARANG<br>KULKARNI,N<br>EHA RAI          | Minimizing Leakage<br>Current Using Cmos<br>Technology for a<br>0.25µm Scvl Based<br>4T Dram Design | Sep-<br>2015 | MINIMIZIN<br>G<br>LEAKAGE<br>CURRENT                              | SELF<br>CONTROLLA<br>BLE<br>VOLTAGE<br>LEVEL<br>TECHNIQUE                                                                                                                                                |

| 17 | XIAOZHE<br>LIU,<br>YONGAN<br>ZHENG       | For Chinese Uhf Rfid<br>Transponder An Ultra<br>Low Power Digital<br>Processor                      | Oct-2015     | LOW<br>POWER<br>BASE<br>BAND<br>PROCESSO<br>R FOR UHF<br>RFID TAG | HIGHLY<br>REUSED<br>REGISTER<br>BANK, LOW<br>FRQUENCY<br>DECODING<br>& SORT<br>ALGORITHM                                                                                                                 |

### Vol 12 Issue 01 2023

### **ISSN NO: 2230-5807**

| 18 | R                            | Signal Processing                                                                                 | Aug-         | ADC                                                 | SUPPLY                                                                                  |

|----|------------------------------|---------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------|

|    | VANITHA,S.<br>THENMOZHI      | Applications design<br>using Low Power<br>Cmos Comparator<br>and Bipolar Cmos<br>Technology       | 2015         |                                                     | BOOSTING,B<br>ODY-<br>DRIVEN<br>TRANSISTO<br>RS,<br>CURRENT<br>MODE<br>DESIGN           |

| 19 | JENIL,RAHU<br>L              | Design&DevelopmentOfEfficientReversibleFloatingPointArithmetic Unit                               | Nov-<br>2015 | REVERSIB<br>LE FPAU                                 | REVERSIBLE<br>LOGIC,QUA<br>NTUM<br>CIRCUIT                                              |

| 20 | TOMOKI,<br>SHINTARO          | A Low Power 6t-4c<br>Non Volatile Memory<br>Using Charge Sharing<br>& Non-Precharge<br>Techniques | Mar-<br>2015 | FRAM                                                | BITLINE<br>NONPRECH<br>ARGE<br>TECHNIQUE,<br>PLATE LINE<br>CHARGE<br>SHARE<br>TECHNIQUE |

| 21 | G KARTHIK<br>REDDY           | Low Power PTL<br>based ALU design<br>using LP- FA Design                                          | Mar-<br>2015 | ALU<br>DESIGN                                       | PASS<br>TRANSISTO<br>R LOGIC                                                            |

| 22 | JAGADEEP<br>KAUR,<br>SHIWANI | Design Of Full Adder<br>Circuit Using Double<br>Gate Mosfet                                       | Oct-<br>2015 | FULL<br>ADDER                                       | DOUBLE<br>GATE PTL                                                                      |

| 23 | BALAMURU<br>GAN V            | Performance Analysis<br>of ADML using<br>Leakage Power<br>Reduction Techniques                    | Jun-<br>2015 | DYNAMIC<br>POWER &<br>LEAKAGE<br>POWER              | DUAL MODE<br>LOGIC<br>APPROACH                                                          |

| 24 | DANIEL,ALE<br>XANDER         | Intra-Operation<br>Dynamic Voltage<br>Scaling                                                     | Apr-<br>2015 | VOTAGE<br>SCALING                                   | INTRA<br>OPERATION<br>DYNAMIC<br>VOLTAGE<br>SCALING                                     |

| 25 | HIPPOLYTE,<br>BHEKISIPHO     | LeakageCurrentMinimization&PowerReductionTechniquesUsingSub-ThresholdDesign                       | Mar-<br>2015 | LEAKAGE<br>POWER<br>REDUCTIO<br>N<br>TECHNIQU<br>ES | SUBTHRESH<br>OLD DESIGN                                                                 |

### **3.** IMPLEMENTATION

The proposed work starts with single bit ALU and single bit power gated ALU, followed by the 4-bit ALU & 8-bit ALU implementations. Figure 2 depicts the MOS model parameters used for the design.

### **ISSN NO: 2230-5807**

| Mos Model 3 parameters |                                       |                          |                           |  |  |  |

|------------------------|---------------------------------------|--------------------------|---------------------------|--|--|--|

| Parameter              | Definition                            | Typical Value 0.12µm     |                           |  |  |  |

|                        |                                       | NMOS                     | pMOS                      |  |  |  |

| VTO                    | Theshold voltage of a long channel    | 0.4V                     | -0.4V                     |  |  |  |

|                        | device, at zero Vbs.                  |                          |                           |  |  |  |

| U0                     | Carrier mobility                      | 0.06 m <sup>2</sup> /V.s | 0.025 m <sup>2</sup> /V.s |  |  |  |

| TOX                    | Gate oxide thickness                  | 3 nm                     | 3 nm                      |  |  |  |

| PHI                    | Surface potential at strong inversion | 0.3V                     | 0.3V                      |  |  |  |

| LD                     | Lateral diffusion into channel        | 0.01µm                   | 0.01µm                    |  |  |  |

| GAMMA                  | Bulk threshold parameter              | 0.4 V <sup>0.5</sup>     | 0.4 V <sup>0.5</sup>      |  |  |  |

| KAPPA                  | Saturation field factor               | 0.01 V <sup>-1</sup>     | 0.01 V <sup>-1</sup>      |  |  |  |

| VMAX                   | Maximum drift velocity                | 150Km/s                  | 100Km/s                   |  |  |  |

| THETA                  | Mobility degradation factor           | 0.3 V <sup>-1</sup>      | 0.3 V <sup>-1</sup>       |  |  |  |

| NSS                    | Substhreshold factor                  | 0.07 V <sup>-1</sup>     | 0.07 V <sup>-1</sup>      |  |  |  |

| W                      | MOS channel width                     | 0.5-20µm                 | 0.5-40µm                  |  |  |  |

| L                      | MOS channel length                    | 0.12µm                   | 0.12µm                    |  |  |  |

Figure 2. MOS model3 parameters for 120nm.

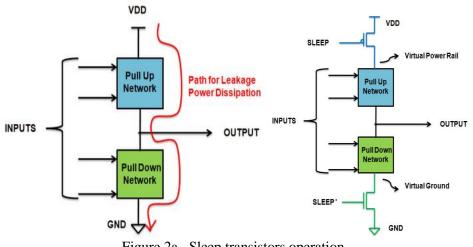

Power gating is effective in reducing power consumption. Power gating is a technique that temporarily shuts down unused circuit blocks to reduce overall chip leakage. This temporary shutdown time is also called "sleep mode" or "inactivity mode". When circuit blocks are needed again for operation, they are activated into "active mode". These two modes are switched at the right time and in the right manner to maximize power performance with minimal performance impact. Therefore, the purpose of power gating is to minimize power leakage by temporarily removing power to selected blocks that are not needed in this mode. Power gating has a greater impact on design architecture than clock gating. The time delay is increased due to the need to safely enter and exit power gated mode. The amount of leakage power savings possible in such low-power modes and the energy dissipation to enter and exit such modes leads to several architectural tradeoffs. Block shutdown can be done in software or hardware. Driver software can schedule shutdown events. You can use a hardware timer. A dedicated power management controller is another option. Power gating uses low-leakage PMOS transistors as header switches to turn off parts of the design in standby or sleep mode. An NMOS footswitch can also be used as a sleep transistor. The insertion of sleep transistors divides the chip's power grid into a permanent power grid connected to the power supply and a virtual power grid that drives the cells and can be switched off. The quality of this complex power grid is critical to a successful power gating design. Two of the most important parameters are IR drop and the cost of silicon area and routing resources. Power gating can be implemented using a cell or cluster-based (or fine-grained) approach, or a distributed coarse-grained approach. Successful implementation of this methodology requires consideration of the following parameters and careful selection of their values. Power Gate Size, Gate Controlled Slew Rate, Simultaneous Switching Capacitance, Power Gate Leakage, Fine Grain Power Gating, Coarse Grain Power Gating.

The ALU performs the basic operations of Add, Sub, Or, And & NOP with the combinations od selection lines S0,S1 respectively. Power gating technique with fine grain methodology is employed as shown in figure 2a.

## Vol 12 Issue 01 2023

### **ISSN NO: 2230-5807**

Figure 2a. Sleep transistors operation.

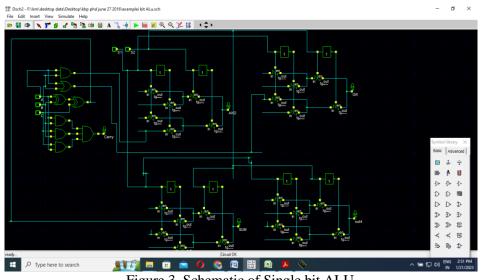

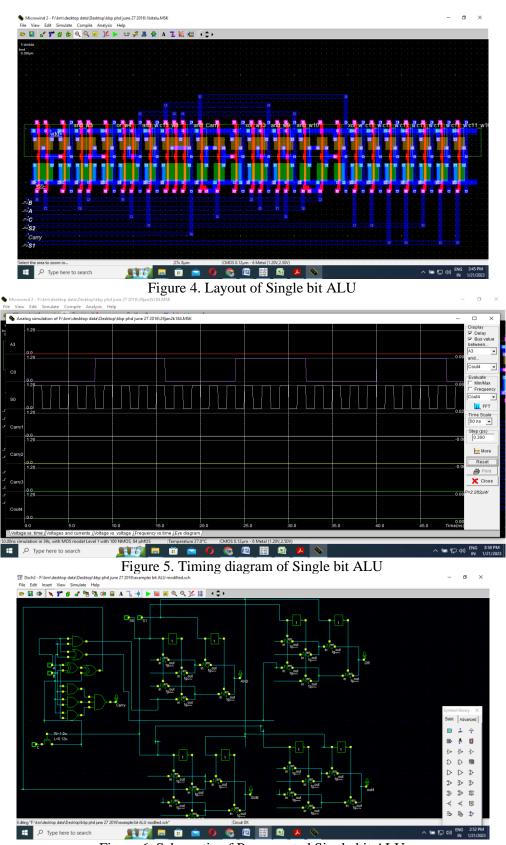

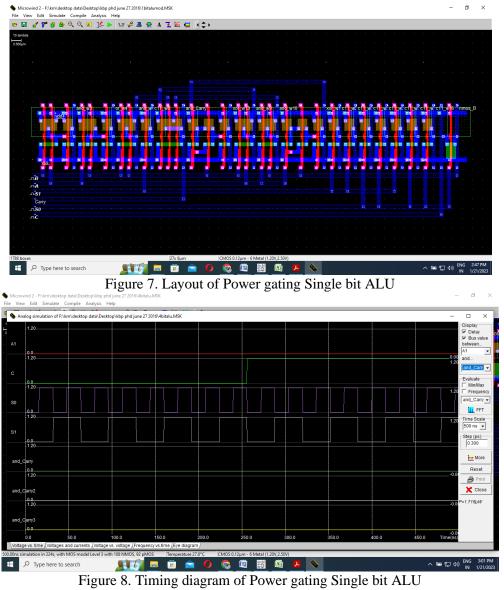

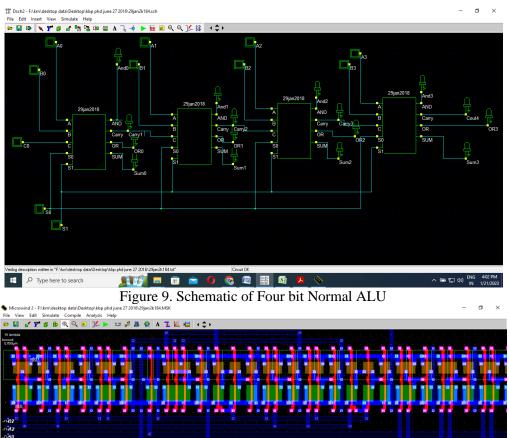

The proposed design of single bit ALU is shown in fig3 and power gated single bit ALU is shown in fig 6.

Figure 3. Schematic of Single bit ALU

### Vol 12 Issue 01 2023

Figure 6. Schematic of Power-gated Single bit ALU

### Vol 12 Issue 01 2023

### Vol 12 Issue 01 2023

👥 👘 🗖 😭 📀 🕐 😨 📰 🛤 🖊 💊

### Vol 12 Issue 01 2023

### **ISSN NO: 2230-5807**

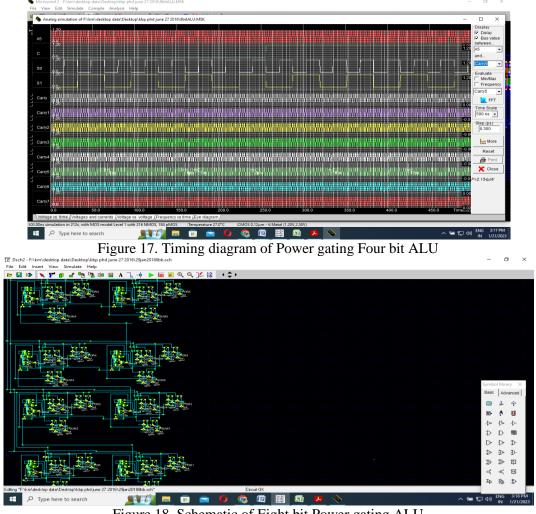

Figure 11. Timing diagram of Normal Four bit ALU

0.0 0.0 0.6 0.5 0.5 🔣 More Reset B Print 0.56 X Close 17.601µW 0.5 😰 🧱 🗄 🔎 Type here to search 💼 🔘 8 X

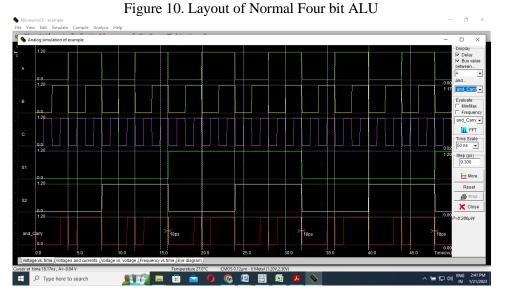

Figure 14. Timing diagram of Normal Eight bit ALU

### Vol 12 Issue 01 2023

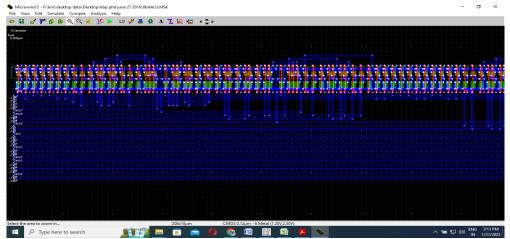

Figure 18. Schematic of Eight bit Power gating ALU

Figure 19. Layout of Power gating Eight bit ALU

### Vol 12 Issue 01 2023

### **ISSN NO: 2230-5807**

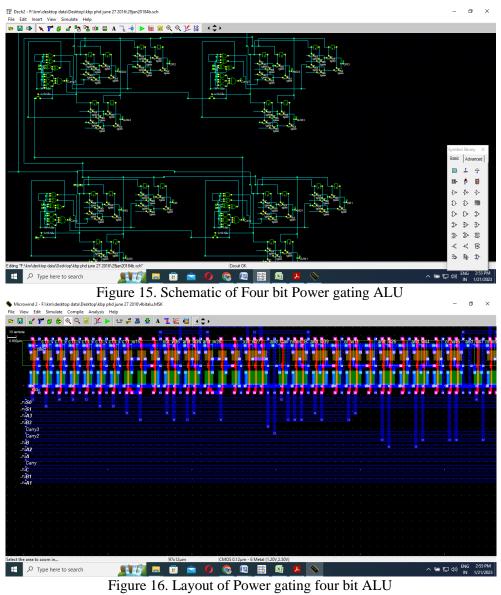

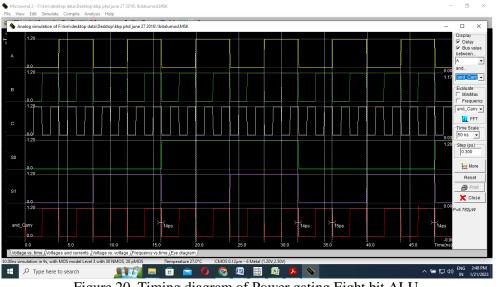

Figure 20. Timing diagram of Power gating Eight bit ALU

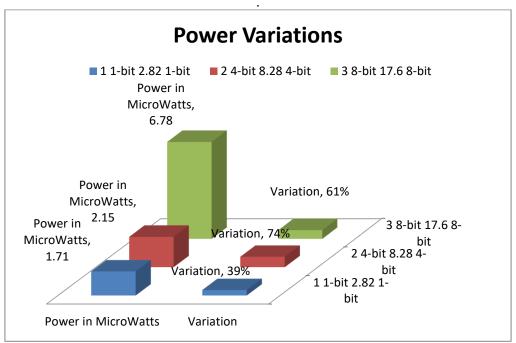

Figure 21. Power dissipation comparisons in µW of Power Gated & Normal ALU

#### CONCLUSIONS

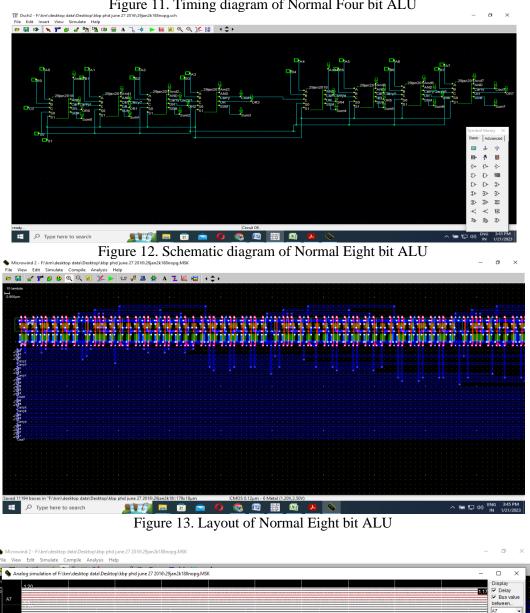

In the proposed design the power dissipations are obtained with 120nm mos3 model files and the tabular form is shown below table3.

| Sl.No | NORMAL-<br>ALU | Power in<br>MicroWatts | POWERGATED-<br>ALU | Power in<br>MicroWatts | Variation |

|-------|----------------|------------------------|--------------------|------------------------|-----------|

| 1     | 1-bit          | 2.82                   | 1-bit              | 1.71                   | 39%       |

| 2 | 4-bit | 8.28 | 4-bit | 2.15 | 74% |

|---|-------|------|-------|------|-----|

| 3 | 8-bit | 17.6 | 8-bit | 6.78 | 61% |

We can conclude that for power-gated ALU design there is around 39-77% variations in power dissipation. In future we can use more number of add-on functions to the ALU and can be effectively replaced with Reversible logic gates, Finfet gates.

#### REFERENCES

- [1] G.SARANYA, R.S. KIRUTHIKA OPTIMIZED DESIGN OF AN ALU BLOCK USING ARCHITECTURAL LEVEL OF POWER OPTIMIZATION TECHNIQUES 3/1/11 IEEE XPLORE 168-172

- [2] N.RAVINDRAN,R.MARY LOURDE AN OPTIMUM VLSI DESIGN OF 16-BIT ALU 3/1/15 IEEE XPLORE 52-55

- [3] GUANG-MINGTANG,KENSUKE TAKATA 4-BIT SLICE ALU FOR 32-BIT RSFQ MICROPROCESSORS 1/1/16 IEEE TRANSACTIONS ON SUPERCONDUCTIVITY VOL 26 NO.1 1112-1120

- [4] JINHUI WANG, NA GONG PNS-FCR:FLEXIBLE CHARGE RECYCLING DYNAMIC CIRCUIT TECHNIQUE FOR LOW POWER MICROPROCESSORS 2/1/16 IEEE TRANSACTIONS ON VLSI VOL 24 NO.2 613-624

- [5] YU-GUANG CHEN,WAN-YU WEN A NOVEL LOW COST DYNAMIC LOGIC RECONFIGURABLE STRUCTURE STRATEGY FOR LOW POWER OPTIMIZATION 8/1/16 IEEE XPLORE 250-255

- [6] CHRISTOPHER SCHAEF, JASON T STAUTHEFFICIENT VOLTAGE REGULATION FOR MICROPROCESSOR CORES STACKED IN VERTICAL VOLTAGE DOMAINS 2/1/16 IEEE TRANSACTIONS ON POWER ELECTRONICS VOL.31.NO.2 1795-1808

- [7] CHENG-YEN LEE,PING-HSUAN HSIES A STANDARD CELL DESIGN FLOW COMPATIBLE ENERGY RECYCLING LOGIC WITH 70% ENERGY SAVING 1/1/16 IEEE TRANSACTIONS ON CIRCUITS & SYSTEMS-1. VOL.63 NO.170-79

- [8] AN-TAI XIAO,YUNG-SIANG MIAO A VARIABLE VOLTAGE LOW POWER TECHNIQUE FOR DIGITAL CIRCUIT SYSTEM 3/1/16 IEEE XPLORE 13-14

- [11] HAKONTOREYIN,PAMELA T BHATTI A LOW POWER ASIC SIGNAL PROCESSOR FOR A VESTIBULAR PROSTHESIS 6/1/16 IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS & SYSTEMS VOL.10.NO 3 768-778

- [12] SMITA SINGHAL,NIDHI GAUR ANALYSIS & COMPARISION OF LEAKAGE POWER REDUCTION TECHNIQUES IN CMOS CIRCUITS 9/1/15 IEEE XPLORE 936-944

- [13] JEFFERSON A HORA,NIEVA M MAPULA DESIGN OF RF TO DC CONVERTER IN 90NM CMOS TECHNOLOGY FOR ULTRA LOW POWER APPLICATION 12/1/15 IEEE XPLORE 121-126

- [14] MANAS SINGHAL, RAJESH MEHRA LAYOUT DEVELOPMENT OF AREA EFFICIENT LO-SKEWED EVEN PARITY GENERATOR 12/1/15 IEEE XPLORE 614-618

- [15] ANDRES GOMEZ, CHRISTIAN PINTO REDUCING ENERGY CONSUMPTION IN MICROCONTROLLER-BASED PLATFORMS WITH LOW DESIGN MARGIN CO-PROCESSORS 10/1/15 IEEE XPLORE 269-272

#### Vol 12 Issue 01 2023

#### **ISSN NO: 2230-5807**

- [16] SARANG KULKARNI,NEHA RAI A 0.25µm SCVL BASED 4T DRAM DESIGN FOR MINIMIZING LEAKAGE CURRENT USING CMOS TECHNOLOGY 9/1/15 IEEE XPLORE 230-233

- [17] XIAOZHE LIU, YONGAN ZHENG AN ULTRA LOW POWER DIGITAL PROCESSOR FOR CHINESE UHF RFID TRANSPONDER 10/1/15 IEEE XPLORE 83-86

- [18] R VANITHA,S.THENMOZHI LOW POWER CMOS COMPARATOR USING BIPOLAR CMOS TECHNOLOGY FOR SIGNAL PROCESSING APPLICATIONS 8/1/15 IEEE XPLORE 1241-1243

- [19] JENIL, RAHUL DESIGN & DEVELOPMENT OF EFFICIENT REVERSIBLE FLOATING POINT ARITHMETIC UNIT 11/1/15 IEEE XPLORE 811-815

- [20] TOMOKI, SHINTARO A LOW POWER 6T-4C NON VOLATILE MEMORY USING CHARGE SHARING & NON-PRECHARGE TECHNIQUES 3/1/15 IEEE XPLORE 2904-2907

- [21] G KARTHIK REDDY LOW POWER PASS TRANSISTOR LOGIC BASED ALU DESIGN USING LOW POWER FULL ADDER DESIGN 3/1/15 IEEE XPLORE 131--136

- [22] JAGADEEP KAUR, SHIWANI DESIGN OF FULL ADDER CIRCUIT USING DOUBLE GATE MOSFET 10/1/15 IEEE XPLORE 57-60

- [23] BALAMURUGAN V PERFORMANCE ANAYSIS OF ASYNCHRONOUS DUAL MODE LOGIC USING LEAKAGE POWER REDUCTION TECHNIQUES 6/1/15 IEEE XPLORE 46-50

- [24] DANIEL,ALEXANDER INTRA-OPERATION DYNAMIC VOLTAGE SCALING 4/1/15 IEEE XPLORE 70-77

- [25] HIPPOLYTE,BHEKISIPHO LEAKAGE CURRENT MINIMISATION & POWER REDUCTION TECHNIQUES USING SUB-THRESHOLD DESIGN 3/1/15 IEEE XPLORE 146-150

K Prasad Babu is working as an Associate Professor in the department of Electronics and Communication Engineering of Ashoka Women's Engineering College, Kurnool, Andhra Pradesh, India. He has 16 years of Teaching experience. He has received his B.Tech from JNTUH, M.Tech from GPREC. Currently he is Research Scholar in ECE Dept with research area as VLSIDesign, JNTUA College of Engineering, Anantapuram, Andhra Pradesh, His research areas of interest includes VLSI, Embedded Systems, Image Processing. He has published several papers in national and international journals.

Dr. K.E.Sreenivasa Murthy is currently working as Principal & Prof, Ravindra College of Engineering for Women, Kurnool, Andhra Pradesh, India. In the year 1989, K.E.Sreenivasa Murthy completed his B.Tech from S.V.University, Andhra Pradesh, In the year 1992 he finished M.Tech from S.V.University, Andhra Pradesh. In 2003 he obtained the PhD degree from S.K.University, Andhra Pradesh Overall experience in teaching is 28 years. His areas of interest

#### Vol 12 Issue 01 2023

#### **ISSN NO: 2230-5807**

include Embedded systems, Microcontrollers. He authored several national, international journals and conference manuscripts. He is life time member of ISTE and Instrumentation Society of India. He is member of IEE and IETE.

Dr M.N. Giri Prasad is working as Director of Academics & Audit, JNTUA, and Professor in the Department of Electronics and Communication Engineering at JNTUA College of Engineering, Anantapur, Andhra Pradesh, India. He received his B.Tech degree from JNTU College of Engineering, Anantapur, Andhra Pradesh, India in the year 1982, M. Tech degree from Sri Venkateswara University, Tirupati, Andhra Pradesh, India in the year 1982, M. Tech degree from J.N.T University, Hyderabad, Andhra Pradesh, India in 2003. He is having more than 32 years of teaching experience. His research areas are Wireless Communications, Biomedical Instrumentation, signal processing, Image processing, embedded systems and microcontrollers. He has published more than 35 papers in national and international conferences. Around 70 papers published in national and international journals. He is a life member of ISTE, IEI and NAFEN.